#### 2.4GHz SPREAD-SPECTRUM TRANSCEIVER

### **Typical Applications**

- IEEE 802.11b WLANs

- Wireless Residential Gateways

- Secure Communication Links

- High Speed Digital Links

- Wireless Security

- Digital Cordless Telephones

#### **Product Description**

The RF2958 is a single-chip transceiver specifically designed for IEEE 802.11b applications. The part includes all required transceiver functions. The receiver includes: an LNA and downconverter; complete synthesizers and VCO's; direct conversion from IF receiver with variable gain control; quadrature demodulator; I/Q baseband amplifiers; and, on-chip baseband filters. For the transmit side, a QPSK modulator and upconverter are provided along with the synthesizer, VCO, and PA driver. A minimum number of external components are required, resulting in an ultra-compact low-cost radio design. Twocell or regulated three-cell (3.6V maximum) battery applications are supported by the part. The RF2958 is also part of a 2.4GHz chipset along with our high-efficiency GaAs HBT PA and the RF3002 Baseband Processor.

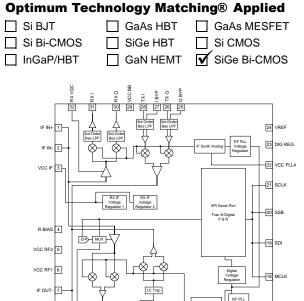

#### **Optimum Technology Matching® Applied**

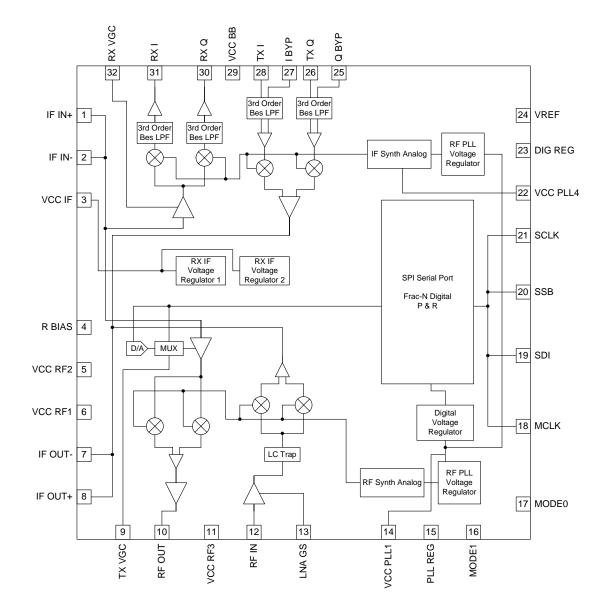

**Functional Block Diagram**

17 MODEC

15 16 VODE

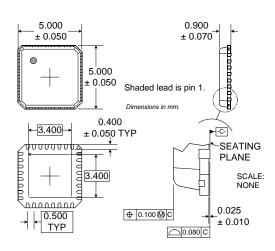

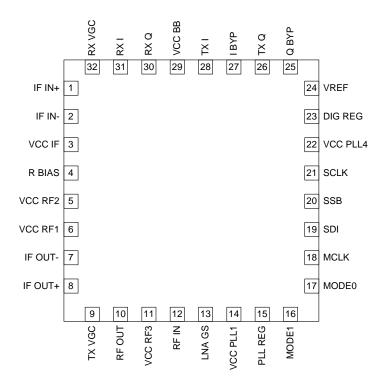

#### Package Style: QFN, 32-Pin, 5x5

#### Features

- Complete IEEE802.11b Transceiver including VCOs

- Small 32-pin Leadless Package

- Minimal External Components Required

- Low Receive Current

- High Performance Super-het Architecture

#### Ordering Information

| RF2958<br>RF2958TR13<br>RF2958 PCBA                         | 2.4GHz Spread-Spectrum<br>2.4GHz Spread-Spectrum<br>Fully Assembled Evaluation | n Transceiver (Tape & Reel)                                     |

|-------------------------------------------------------------|--------------------------------------------------------------------------------|-----------------------------------------------------------------|

| RF Micro Devices,<br>7628 Thorndike Ro<br>Greensboro, NC 27 | ad                                                                             | Tel (336) 664 1233<br>Fax (336) 664 0454<br>http://www.rfmd.com |

IF OUT+ 8

#### **Absolute Maximum Ratings**

| Parameter                     | Rating       | Unit            |

|-------------------------------|--------------|-----------------|

| Supply Voltage                | -0.5 to +3.6 | V <sub>DC</sub> |

| Control Voltages              | -0.5 to +3.6 | V <sub>DC</sub> |

| Input RF Level                | +12          | dBm             |

| Operating Ambient Temperature | -40 to +85   | °C              |

| Storage Temperature           | -40 to +150  | °C              |

Refer to "Handling of PSOP and PSSOP Products" on page 16-15 for special handling information.

Refer to "Soldering Specifications" on page 16-13 for special soldering information.

RF Micro Devices believes the furnished information is correct and accurate at the time of this printing. However, RF Micro Devices reserves the right to make changes to its products without notice. RF Micro Devices does not assume responsibility for the use of the described product(s).

| Parameter                |                        | Specificatio           | n                     | Unit              | Condition                                                                                               |

|--------------------------|------------------------|------------------------|-----------------------|-------------------|---------------------------------------------------------------------------------------------------------|

| Parameter                | Min.                   | Тур.                   | Max.                  |                   | Condition                                                                                               |

| Receiver LNA/RF          |                        |                        |                       |                   | V <sub>CC</sub> =3.0V, T=+25°C, MCLK=44MHz,<br>unless otherwise specified                               |

| RF Frequency Range       | 2400                   |                        | 2500                  | MHz               |                                                                                                         |

| IF Frequency Range       | 363                    |                        | 385                   | MHz               | 374MHz ±11MHz                                                                                           |

| Voltage Gain - High      | 32<br>(20dB<br>power)  | 35<br>(23dB<br>power)  | 38<br>(26dB<br>power) | dB                | LNA/mixer voltage gain (Note: into output<br>impedance). LNA/mixer/SAW filter voltage<br>gain. LNA GS=1 |

| Voltage Gain - Low       | -1<br>(-13dB<br>power) | +2<br>(-10dB<br>power) | +5<br>(-7dB<br>power) | dB                | LNA/mixer voltage gain. LNA GS=0                                                                        |

| Noise Figure - High Gain | . ,                    | 4                      | . ,                   | dBm               |                                                                                                         |

| Noise Figure - Low Gain  |                        | 32                     |                       | dBm               |                                                                                                         |

| Input IP3 - High Gain    | -23                    |                        |                       | dBm               |                                                                                                         |

| Input IP3 - Low Gain     | +8                     |                        |                       | dBm               |                                                                                                         |

| Input P1dB - High Gain   | -30                    |                        |                       | dBm               |                                                                                                         |

| Input P1dB - Low Gain    | -2                     |                        |                       | dBm               |                                                                                                         |

| Input Return Loss        |                        | 10                     |                       | dB                | Z <sub>0</sub> =50Ω                                                                                     |

| Output Impedance         |                        | 750                    |                       | Ω                 |                                                                                                         |

| Image Rejection          | 30                     |                        |                       | dB                |                                                                                                         |

| Receiver                 |                        |                        |                       |                   |                                                                                                         |

| IF VGA/Baseband          |                        |                        |                       |                   |                                                                                                         |

| IF Frequency Range       |                        | 374                    |                       | MHz               |                                                                                                         |

| IF Input Impedance       |                        | 750                    |                       | Ω                 |                                                                                                         |

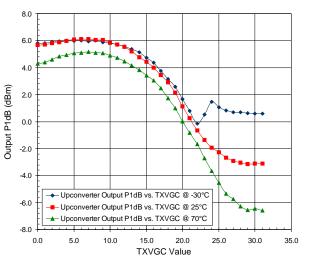

| Voltage Gain - High      | 70                     |                        |                       | dB                | V <sub>GC</sub> =1.25V (measured to single-ended out-<br>put)                                           |

| Voltage Gain - Low       | 4                      |                        |                       | dB                | V <sub>GC</sub> =1.95V (measured to single-ended output)                                                |

| Gain Accuracy            |                        | ±3                     |                       | dB                | For a given RX VGC voltage, the measured gain should lie within ±3dB of ideal                           |

| Gain Response Time       |                        |                        | 300                   | ns                | Measured with a DC step from 1.3V to 1.8V to 90% final value (within 1dB)                               |

| Gain Flatness            | -0.25                  |                        | +0.25                 | dB                | 374MHz ±11MHz, relative to gain at 374MHz                                                               |

| Input Referred Noise     |                        |                        | 11                    | uV <sub>RMS</sub> | Measured into the IF VGA pin.                                                                           |

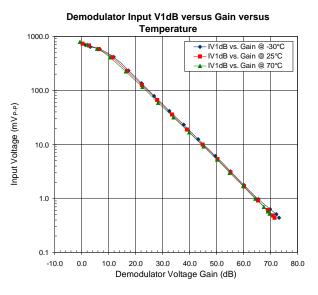

| Input V1dB               | 500                    |                        |                       | mV <sub>P-P</sub> | 1 dB compression of IF strip.                                                                           |

| Output Distortion        |                        | 1.0                    |                       | %                 | Measured at input to RF3002 single-ended.                                                               |

| Output Voltage           |                        | 0.75                   |                       | V <sub>P-P</sub>  | Single-ended.                                                                                           |

| Output V1dB              |                        | 1.25                   |                       | V <sub>P-P</sub>  |                                                                                                         |

| Parameter                       |      | Specificatio | n     | Unit              | O an dition                                                                                           |

|---------------------------------|------|--------------|-------|-------------------|-------------------------------------------------------------------------------------------------------|

| Falailletei                     | Min. | Тур.         | Max.  | Unit              | Condition                                                                                             |

| Receiver                        |      |              |       |                   |                                                                                                       |

| IF VGA/Baseband, cont'd         |      |              |       |                   |                                                                                                       |

| Group Delay                     |      | 15           |       | ns                |                                                                                                       |

| Filter Rejection                |      |              |       | dB                | Transfer function - 3 pole Bessel at 9MHz                                                             |

| Output Impedance                |      | 20           |       | Ω                 | f<1MHz                                                                                                |

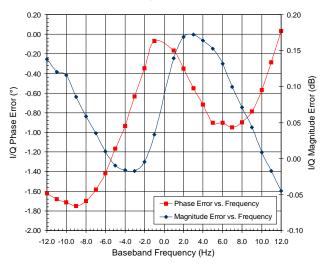

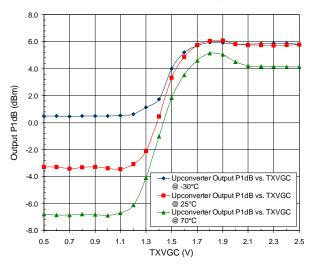

| I/Q Magnitude Error             |      |              | ±0.35 | dB                |                                                                                                       |

| I/Q Phase Error                 |      |              | ±3.0  | ٥                 |                                                                                                       |

| I/Q DC Offset                   |      |              | 10    | mV                | S <sub>QRT</sub> [(V <sub>OUTI</sub> -V <sub>REF</sub> )^2+(V <sub>OUTQ</sub> -V <sub>REF</sub> )^2)] |

| DC Step                         |      |              | 40    | mV                | VGC step 1.3V to 1.8V, P <sub>IN</sub> =-50dBm                                                        |

| V <sub>REF</sub>                | 1.65 | 1.7          | 1.75  | V                 | 3% variation                                                                                          |

| V <sub>REF</sub> Output Current | 1.0  |              |       | mA                | Source                                                                                                |

| Transmitter                     |      |              |       |                   |                                                                                                       |

| Modulator/Baseband              |      |              |       |                   |                                                                                                       |

| I/Q Magnitude Error             |      |              | ±0.35 | dB                |                                                                                                       |

| I/Q Phase Error                 |      |              | ±3.0  | ٥                 |                                                                                                       |

| Input Signal (Single-Ended)     |      | 200          |       | mV <sub>P-P</sub> |                                                                                                       |

| Input Signal Magnitude          |      | 282          |       | mV <sub>P-P</sub> | SQRT(I^2+Q^2)                                                                                         |

| Input P1dB                      | 566  |              |       | mV <sub>P-P</sub> | 6dB from input                                                                                        |

| Voltage Gain to IF              | 4    | 6            | 8     | dB                | Measure from complex magnitude to $IFV_{P-P}$                                                         |

| Output Voltage                  | 448  | 564          | 710   | mV <sub>P-P</sub> |                                                                                                       |

| Output SNR                      |      | 32           |       | dB                | Connected to SAW filter                                                                               |

| Carrier Leakage                 |      |              | -20   | dBc               | Single sideband modulation                                                                            |

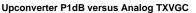

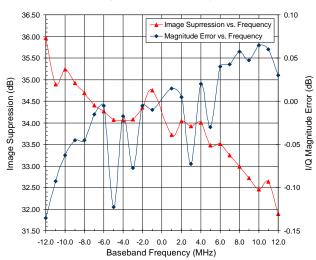

| VGA Driver/Upconverter          |      |              |       |                   |                                                                                                       |

| Input P1dB                      | 550  |              |       | mV <sub>P-P</sub> | 6dB from max input                                                                                    |

| Input Referred Noise            |      |              | 20    | uV <sub>RMS</sub> | Measured in 11 MHz bandwidth at 2.442 GHz<br>upconverter gain >12 dB                                  |

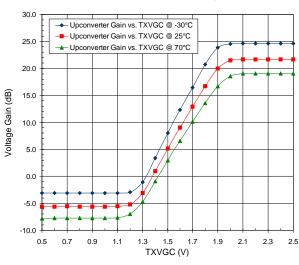

| Minimum Gain                    |      |              | 0     | dB                | TX VGC at 1.3V                                                                                        |

| Maximum Gain                    | 17   |              |       | dB                | TX VGC at 1.9V                                                                                        |

| Gain Response Time              |      |              | 300   | ns                | Measured with 300 mV change in gain on TXVGC to 90% of final P <sub>OUT</sub> .                       |

| Image Rejection                 | 30   |              |       | dB                |                                                                                                       |

| RF LO Leakage                   | -25  | -36          |       | dBm               | F <sub>LO</sub> =2048MHz to 2110MHz                                                                   |

| Output Voltage                  |      |              | 1000  | mV <sub>P-P</sub> | 802.11b output with 7dB to 20dB gain (needed for +20dBm P <sub>OUT</sub> ).                           |

| Minimum Output Power            |      |              | -12   | dBm               | TXVGC at 1.3V                                                                                         |

| Maximum Output Power            | 0    |              |       | dBm               | Meeting 802.11b Spectral Mask                                                                         |

| Parameter                                           |                    | Specificatio | n                  | l la it | Condition                                                                                                                                               |

|-----------------------------------------------------|--------------------|--------------|--------------------|---------|---------------------------------------------------------------------------------------------------------------------------------------------------------|

| ו מומוווכוכו                                        | Min.               | Тур.         | Max.               | Unit    | Condition                                                                                                                                               |

| Digital Input                                       |                    |              |                    |         |                                                                                                                                                         |

| Specifications                                      |                    |              |                    |         |                                                                                                                                                         |

| Apply to pins: SSB, SDI, SCLK,<br>MODE0, MODE1      |                    |              |                    |         |                                                                                                                                                         |

| Input High Voltage (V <sub>IH</sub> )               | 0.7V <sub>DD</sub> |              |                    | V       |                                                                                                                                                         |

| Input Low Voltage (V <sub>IL</sub> )                |                    |              | 0.3V <sub>DD</sub> | V       |                                                                                                                                                         |

| Input High Static Current (I <sub>IH</sub> )        |                    |              | 5                  | μA      |                                                                                                                                                         |

| Input Low Static Current (III)                      |                    |              | 5                  | μA      |                                                                                                                                                         |

| Reset Time                                          |                    | 50           |                    | μS      | Exiting Reset mode or using SPI Reset                                                                                                                   |

| Apply to pins: SSB, SDI, SCLK                       |                    |              |                    | •       |                                                                                                                                                         |

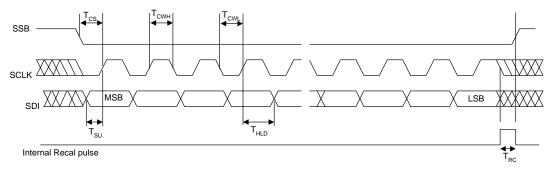

| Input Setup Time (T <sub>SU</sub> )*                | 5                  |              |                    | ns      |                                                                                                                                                         |

| Input Hold Time (T <sub>HLD</sub> )*                | 5                  |              |                    | ns      |                                                                                                                                                         |

| Input Rise/Fall Time (T <sub>RFI</sub> )            |                    |              | 5                  | ns      |                                                                                                                                                         |

| Input Clock to Select Time (T <sub>CS</sub> )       | 5                  |              |                    | ns      |                                                                                                                                                         |

| Input Clock Pulse Width High<br>(T <sub>CWH</sub> ) | 22                 |              |                    | ns      |                                                                                                                                                         |

| Input Clock Pulse Width Low<br>(T <sub>CWL</sub> )  | 22                 |              |                    | ns      |                                                                                                                                                         |

| PLL Recalibration Pulse Width<br>(T <sub>RC</sub> ) | 1/fr               |              |                    | S       | For fr=22MHz, $T_{RC}$ is 45.5ns minimum                                                                                                                |

| Digital Driver Output                               |                    |              |                    |         |                                                                                                                                                         |

| Apply to pin: SDI (output mode)                     |                    |              |                    |         |                                                                                                                                                         |

| Output High Voltage (V <sub>OH</sub> )              | 0.8V <sub>DD</sub> |              |                    | V       | With 1 mA load                                                                                                                                          |

| Output Low Voltage (V <sub>OL</sub> )               |                    |              | $0.2V_{DD}$        | V       | With 1 mA load                                                                                                                                          |

| Output Rise/Fall Time (T <sub>RFO</sub> )           |                    |              | 5                  | ns      | With 20pF maximum load capacitance mea-<br>sured from 10% to 90% of output voltage                                                                      |

| Output Current Source ( I <sub>OH</sub>  )          | 3.8                |              |                    | mA      | Output at (V <sub>DD</sub> -0.3V)                                                                                                                       |

| Output Current Sink ( I <sub>OL</sub>  )            | 10                 |              |                    | mA      | Output at 0.3V                                                                                                                                          |

| MCLK Input (AC-Coupled)                             |                    |              |                    |         | MCLK can be driven DC-coupled by a<br>CMOS clock oscillator with rail-to-rail out-<br>puts. Other oscillator configurations may<br>require AC-coupling. |

| Apply to pin: MCLK                                  | 500                |              |                    |         |                                                                                                                                                         |

| Peak-to-Peak Input Voltage<br>(V <sub>P-P</sub> )   | 500                |              |                    | mV      |                                                                                                                                                         |

| DC Bias at MCLK (MCLK_DC)                           | 0.6                |              | 1.1                | V       |                                                                                                                                                         |

| Specification Valid Range                           | 20                 |              | . 70               | *       |                                                                                                                                                         |

| Temperature<br>Supply Voltage                       | -30<br>2.7         | 3.0          | +70<br>3.6         | °C<br>V |                                                                                                                                                         |

| Transmit Current                                    | 2.7<br>50          | 3.0<br>68    | 3.6<br>80          | mA      | MODE0=0, MODE1=1                                                                                                                                        |

| Receive Current                                     | 30                 | 52           | 60                 | mA      | MODE0=0, MODE1=1<br>MODE0=1, MODE1=0                                                                                                                    |

| Idle Current                                        | 5                  | 28           | 40                 | mA      | MODE0=0, MODE1=0                                                                                                                                        |

| Reset Current                                       | _                  | 1            | 2                  | mA      | MODE0=0, $MODE1=0MODE0=1$ , $MODE1=1$                                                                                                                   |

| Hibernate Current                                   |                    | 0.2          | 0.5                | mA      |                                                                                                                                                         |

\*Setup and Hold Times are measured from the time where the waveforms cross VDD/2.

#### **Digital Timing Specifications**

| Pin         | Function      | Description                                                                                                                                                                                                                                         |  |  |  |  |  |

|-------------|---------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| 1           | IF IN+        | Differential input from IF SAW filter. See application schematic for matching circuit.                                                                                                                                                              |  |  |  |  |  |

| 2           | IF IN-        | See pin 1.                                                                                                                                                                                                                                          |  |  |  |  |  |

| 3           | VCC IF        | Power supply for IF circuitry. Provide 330 pF bypass capacitor close to this pin.                                                                                                                                                                   |  |  |  |  |  |

| 4           | R BIAS        | Bandgap voltage reference for on-chip biasing. Install a 22.1 k $\Omega$ , 1% resistor from this pin to ground.                                                                                                                                     |  |  |  |  |  |

| 5           | VCC RF2       | Power supply for TX and RX bias, LO buffers and mixers. Provide 6pF bypass capacitor close to this pin.                                                                                                                                             |  |  |  |  |  |

| 6           | VCC RF1       | See pin 5.                                                                                                                                                                                                                                          |  |  |  |  |  |

| 7           | IF OUT-       | Differential output to IF SAW filter. See application schematic for matching circuit.                                                                                                                                                               |  |  |  |  |  |

| 8           | IF OUT+       | See pin 7.                                                                                                                                                                                                                                          |  |  |  |  |  |

| 9           | TX VGC        | X analog gain control. Depending on desired operation mode, transmitter gain can be controlled through his pin or the three-wire digital interface. This pin can also provide a bias voltage to an external PA. See heory of operation for details. |  |  |  |  |  |

| 10          | <b>RF OUT</b> | TX PA driver output.                                                                                                                                                                                                                                |  |  |  |  |  |

| 11          | VCC RF3       | Power supply for LNA and TX output driver. Power should be connected to this pin through an inductor or a long $50\Omega$ transmission line RF-shorted with a 6pF capacitor at the other end.                                                       |  |  |  |  |  |

| 12          | RF IN         | RX input from antenna.                                                                                                                                                                                                                              |  |  |  |  |  |

| 13          | LNA GS        | Gain select pin for the internal LNA. High-gain operation is selected when this pin is a logic '1'.                                                                                                                                                 |  |  |  |  |  |

| 14          | VCC PLL1      | Power supply for the PLL RF LO synthesizer. Provide 0.01 µF and 6pF bypass capacitors close to this pin.                                                                                                                                            |  |  |  |  |  |

| 15          | PLL REG       | Internal PLL regulator output. Bypass with 10nF capacitor. Do not connect to V <sub>CC</sub> or ground.                                                                                                                                             |  |  |  |  |  |

| 16          | MODE1         | Controls operational state of the device. See Theory of Operation section for details.                                                                                                                                                              |  |  |  |  |  |

| 17          | MODE0         | See pin 16.                                                                                                                                                                                                                                         |  |  |  |  |  |

| 18          | MCLK          | Reference oscillator for the PLL synthesizer.                                                                                                                                                                                                       |  |  |  |  |  |

| 19          | SDI           | Data signal for the synchronous three-wire digital control interface.                                                                                                                                                                               |  |  |  |  |  |

| 20          | SSB           | Chip select signal for the synchronous three-wire digital control interface.                                                                                                                                                                        |  |  |  |  |  |

| 21          | SCLK          | Clock signal for the synchronous three-wire digital control interface.                                                                                                                                                                              |  |  |  |  |  |

| 22          | VCC PLL4      | Power supply for the PLL IF LO synthesizer. Provide 0.01 µF and 330 pF bypass capacitors close to this<br>bin.                                                                                                                                      |  |  |  |  |  |

| 23          | DIG REG       | Internal digital regulator output. Bypass with 10nF capacitor. Do not connect to $V_{CC}$ or ground.                                                                                                                                                |  |  |  |  |  |

| 24          | VREF          | I/Q DC reference voltage for the baseband processor. This pin should be connected to a high impedance on the baseband processor.                                                                                                                    |  |  |  |  |  |

| 25          | Q BYP         | Baseband differential input signal for the TX quadrature channel. For single-ended applications, bypass to ground with a $0.01\mu\text{F}$ capacitor.                                                                                               |  |  |  |  |  |

| 26          | TX Q          | Baseband input signal for the TX quadrature channel.                                                                                                                                                                                                |  |  |  |  |  |

| 27          | I BYP         | Baseband differential input signal for the TX in-phase channel. For single-ended applications, bypass to ground with a 0.01 $\mu F$ capacitor.                                                                                                      |  |  |  |  |  |

| 28          | ΤΧΙ           | Baseband input signal for the TX in-phase channel.                                                                                                                                                                                                  |  |  |  |  |  |

| 29          | VCC BB        | Power supply for baseband circuitry. Provide 0.01 µF bypass capacitor close to this pin.                                                                                                                                                            |  |  |  |  |  |

| 30          | RX Q          | Baseband output signal for the RX quadrature channel.                                                                                                                                                                                               |  |  |  |  |  |

| 31          | RXI           | Baseband output signal for the RX in-phase channel.                                                                                                                                                                                                 |  |  |  |  |  |

| 32          | RX VGC        | Analog gain control for the RF IF amplifier.                                                                                                                                                                                                        |  |  |  |  |  |

| Pkg<br>Base | GND           | Device ground. Connect directly to PCB ground plane.                                                                                                                                                                                                |  |  |  |  |  |

|             | ESD           | All pins except pin 12 are provided with electrostatic discharge protection to 3kV using the human body model.                                                                                                                                      |  |  |  |  |  |

**Pin Out**

### **Detailed Functional Block Diagram**

### **Theory of Operation**

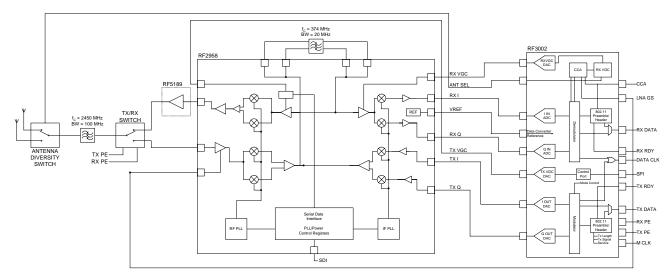

The RF2958 is a single-chip transceiver designed specifically for IEEE 802.11b wireless LAN applications. In addition to typical transceiver functions of RF conversion of both the transmit and receive signals, the RF2958 incorporates a low-noise amplifier (LNA) and a dual phase-locked loop (PLL) frequency synthesizer to reduce end-product component count and to simplify integration into end-products. The RF2958 uses a superheterodyne frequency conversion architecture in both the transmit and receive signal paths for superior performance in 802.11b applications. It also incorporates power conservation functionality to increase battery life in portable and mobile applications. When used with the RF3002 baseband processor and RF5189 power amplifier (PA), the RF2958 is part of a complete PHY solution for 802.11b applications (see figure below, 2.4GHz IEEE 802.11b Chipset Block Diagram).

#### SYSTEM ARCHITECTURE

The overall system architecture is based around a superheterodyne conversion process. For the transmitter side, the baseband in-phase (I) and quadrature (Q) signal components are converted to an intermediate frequency (IF) of 374MHz. An external SAW filter is used to filter out undesired spurious frequencies. The IF is then converted to the overthe-air radio frequency (RF) between 2.412GHz and 2.483GHz using low-side injection. The RF output drives a PA to amplify the signal to the desired power level at the antenna. Generally the PA is followed by a TX/RX switch and a band pass filter which eliminates the undesired sideband resulting from the mixing process before broadcasting the signal through the antenna.

The receiver is the inverse of this process. The signal from the antenna passes through the band pass filter, which is in this case acting as a pre-selection filter. The received signal passes through the integrated LNA and is converted to an IF of 374MHz. The signal then passes through a SAW filter, which acts to reject adjacent channels as defined by the 802.11 standard. Due to the bandwidth of this filter, adjacent channels must be at least 20MHz apart. The filtered IF signal is then downconverted to baseband I and Q components.

The local oscillators required by the mixing process are generated by internal IF and RF PLL frequency synthesizers. These are controlled through a three-wire serial data interface.

#### **GENERAL APPLICATION INFORMATION**

This part is used at high frequencies. Proper attention to layout and component selection is critical in order to achieve the specified performance. Values for DC blocking capacitors and power supply bypass capacitors should be selected so that they are series self-resonant at the frequency of operation. In addition, transmission line techniques should always be used on signal lines at RF frequencies, and may be required on signal lines at IF frequencies if connections are long with respect to wavelength.

The RF2958 should be powered from regulated supply. If not sharing this supply with the MCLK oscillator, the MCLK oscillator should also be powered from a well-regulated supply. Avoid sharing the RF2958 and MCLK oscillator supplies with the baseband processor and/or MAC.

Power supply bypassing of VCC lines for the PLL is critical in order to minimize the effects of power supply noise on phase noise performance. In addition to RF/IF bypassing, these lines should be bypassed with low-frequency capacitors. A value of  $0.01 \,\mu\text{F}$  is sufficient for most applications, but performance should be verified by looking at a modulated signal on a vector signal analyzer or a constant signal on a spectrum analyzer or phase noise test set.

Since this is a mixed-signal device, care should be taken to separate traces connecting to digital circuits from those connecting to analog circuits. Power supply bypassing is important to keep the noise contributions of digital circuits to a minimum. It is generally better to start with more bypassing than you think you need, then remove components and reevaluate performance.

#### ENABLE/DISABLE MODES

Operation of the device is controlled by the MODE0 and MODE1 pins according to the following truth table.

| MODE0 | MODE1 | Function        |

|-------|-------|-----------------|

| 0     | 0     | Idle            |

| 0     | 1     | Transmit Enable |

| 1     | 0     | Receive Enable  |

| 1     | 1     | Reset           |

When switching between modes, ensure that MODE0 and MODE1 are high for less than three master clock cycles to avoid inadvertently entering reset modes. To enter reset mode, ensure that MODE0 and MODE1 are high for at least five master clock cycles.

In Idle mode, the IF and RF PLLs are locked and the baseband circuitry is powered; everything else is disabled. In Reset mode, the voltage regulators for the digital circuitry inside the part are enabled; everything else is disabled.

Additionally, there is a hibernate mode in which everything is disabled. This mode is entered by writing the value 8h to Register 0 while in hibernate mode. The MODE0 and MODE1 pins should be held high while in hibernate mode. To exit this mode, toggle the states of one or both MODE pins. All registers will need to be reprogrammed on exiting hibernate mode.

#### RECEIVER

#### Front End LNA/Mixer

The LNA/Mixer provides 35dB conversion gain to IF in high-gain mode to detect weak signals at the antenna. In low-gain mode, the LNA/Mixer provides 2dB conversion gain. The LNA GS pin selects gain mode. When LNA GS is high, the part is in high-gain mode. The mixer output is connected to the IF OUT pins as a differential signal for connecting to an external SAW filter. Proper matching at the input and output of the SAW filter is essential for maintaining performance through the system. The IF input and output differential impedances are 750 $\Omega$  nominal.

The same filter is used for transmitter and receiver. Internal switches control which signal is present at the SAW filter. If AC-coupling is required for the SAW filter, use values less than 150pF to ensure that switching speed will not be seriously degraded.

#### IF/Baseband

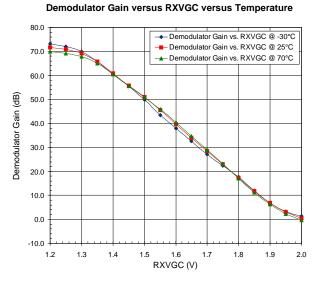

The filtered IF signal is processed through a variable gain amplifier controlled through the RX VGC pin. The IF signal is then downconverted to baseband I and Q signals, which are then filtered on-chip with third order Bessel filters. The IF-to-baseband conversion gain range is 4dB to 72dB depending on the voltage present on the RX VGC pin. The gain slope is negative over a range of 1.2V to 2.0V.

The single-ended I and Q outputs should be DC-coupled to the baseband processor. The DC reference voltage should be provided to the baseband processor through the VREF pin to eliminate the potential for a signal blocker at DC.

#### TRANSMITTER

The I and Q inputs are differential. To use single-ended inputs, place  $0.01 \,\mu\text{F}$  capacitors at the I BYP and Q BYP pins. The inputs should be DC-coupled from the baseband processor. In order to improve carrier suppression at RF, the DC reference voltage should be provided to the baseband processor through the VREF pin. The baseband input signals are filtered on-chip using third order Bessel filters for spectral shaping. The signals are then complex upconverted to IF. The IF mixer output is amplified and connected to the IF OUT pins as a differential signal for connecting to the external SAW filter as described above.

The differential signal from the SAW filter is then amplified using a variable gain amplifier. The gain of this amplifier can be controlled either through the analog TX VGC pin or digitally from the baseband processor or MAC, depending on application. The signal is then upconverted to the desired RF output frequency and amplified to a level appropriate to drive a PA to the desired output level at the antenna.

In order to further extend battery life, the TX VGC pin can be used to control the bias of the external PA. If the user of the end-product determines that he/she does not require full output power, the PA bias and the gain of the IF variable gain amplifier can be controlled by the RF2958 to reduce the current consumption of the PA, thereby increasing battery life. Contact RFMD Applications Engineering for guidance on implementing this feature.

#### DUAL FREQUENCY SYNTHESIZER

#### IF LO PLL

The IF PLL is an integer-N PLL nominally programmed to a center frequency of 748MHz. This frequency is divided by two at the IF converter. A 44MHz oscillator is required to provide the PLL reference frequency through the MCLK pin. See the Register Details and Serial Data Interface sections for details on programming.

#### RF LO PLL

The RF LO PLL is a fractional-N PLL programmed to an appropriate frequency to convert the 374MHz IF to the desired RF channel. The nominal step size is 22MHz with a fractional modulus of 2<sup>24</sup>. The 44MHz reference frequency is divided to the appropriate step size. See the Register Details and Serial Data Interface sections for details on programming.

Note: To ensure proper operation of the PLLs, program Register 12 [17:16] to '11b'. All other bits in Register 12 should be set to '0'.

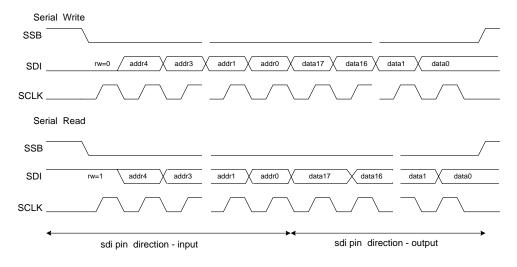

#### SERIAL DATA INTERFACE

A three wire serial data interface allows user programming of the internal control registers in the RF2958. The serial data interface consists of the serial select (SSB), serial data in (SDI) and serial clock (SCLK) pins. The SDI is a bi-directional pin, by default it is configured as an input to the serial interface, but during a read session it is used as an output.

The first bit in a serial transfer (the MSB) is the read/write (R/W) bit. R/W = 1 for a read, and R/W = 0 for a write.

The figure below shows a timing diagram for a serial transfer to the RF2958 serial data interface. The serial select (SSB) pin is normally high. A serial transfer is initiated by taking SSB low. The address and data bits on the serial data in (SDI) pin are shifted in on rising edges of the serial clock (SCLK) pin, MSB first. The data is latched and changes take effect on the falling edge of the clock pulse corresponding to the last (18<sup>th</sup>) data bit in the addressed register. If the transfer is interrupted, such that the 18<sup>th</sup> data bit clock pulse does not occur, then no data is written to the register.

When the synthesizers are programmed, an internal pulse is generated alerting the synthesizer that a new setting is required. In order to guarantee that this internal pulse is long enough, the time between the falling edge of the last serial clock pulse and the rising edge of SSB must be at least 1/fr.

The RF2958 can be reset to its power on condition (including register defaults) by writing '011111b' plus 18 don't care bits to the serial data interface. The reset is actually performed when the SSB is raised after the write. Although this command can be performed during any settings of the MODE0 and MODE1 pins, care should be taken to ensure that the registers are reprogrammed in a sufficient time to perform any transmit or receive operations.

#### **REGISTER DETAILS**

The individual registers and bits are described below. A write instruction to address 11111 causes global reset. All programming values are binary unless otherwise specified.

| Location    | Bit Name          | Default | Function                                                                                                                                                     |

|-------------|-------------------|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CFG1(17:16) | reserved          | 00      | Reserved, program to zero (0)                                                                                                                                |

| CFG1(15:14) | REF_SEL(1:0)      | 00      | Reference Divider Value Divide by 2 1/2 high, 1/2 low   0 0 Divide by 3 1/3 high, 2/3 low   1 0 Divide by 44 1/44 high, 43/44 low   1 1 Divide by 1 (bypass) |

| CFG1(3)     | HYBERNATE         | 0       | Sleep Mode Current<br>0=nominal sleep mode current<br>1=very low sleep mode current                                                                          |

| CFG1(2)     | RF_VCO_<br>REG_EN | 1       | RF VCO Regulator Enable<br>0=disabled<br>1=enabled                                                                                                           |

| CFG1(1)     | IF_VCO_<br>REG_EN | 1       | IF VCO Regulator Enable<br>0=disabled<br>1=enabled                                                                                                           |

| CFG1(0)     | IF_VGA_<br>REG_EN | 1       | IF VGA Regulator Enable<br>0=disabled<br>1=enabled                                                                                                           |

Configuration Register 1 (CFG1)-Address 00000

#### IF PLL Register 1 (IFPLL1)-Address 00001

| Location    | Bit Name  | Default | Function                                                            |

|-------------|-----------|---------|---------------------------------------------------------------------|

| IFPLL1(17)  | PLL_EN1   | 0       | IF PLL Enable                                                       |

|             |           |         | 0=disabled                                                          |

|             |           |         | 1=enabled                                                           |

| IFPLL1(16)  | KV_EN1    | 0       | IF PLL KV Calibration Enable                                        |

|             |           |         | 0=disabled                                                          |

|             |           |         | 1=enabled                                                           |

| IFPLL1(15)  | VTC_EN1   | 1       | IF PLL Coarse Tune Enable                                           |

|             |           |         | 0=VCO coarse tuning system is disabled                              |

|             |           |         | 1=VCO coarse tuning system is enabled                               |

| IFPLL1(14)  | LPF1      | 0       | IF PLL Loop Filter Bypass                                           |

|             |           |         | 0=Internal loop filter is used                                      |

|             |           |         | 1=Internal loop filter is bypassed and External loop filter is used |

| IFPLL1(13)  | CPL1      | 0       | IF PLL Charge Pump Leakage Current                                  |

|             |           |         | 0=minimum value                                                     |

|             |           |         | 1=2xminimum value                                                   |

| IFPLL1(12)  | PDP1      | 1       | IF PLL Phase Detector Polarity                                      |

|             |           |         | 0=positive, VCO frequency increases with increasing tuning voltage  |

|             |           |         | 1=negative, VCO frequency decreases with increasing tuning voltage  |

| IFPLL1(11)  | AUTOCAL_  | 0       | IF PLL Auto Calibration Enable                                      |

|             | EN1       |         | 0=disabled                                                          |

|             |           |         | 1=enabled                                                           |

| IFPLL1(10)  | LD_EN1    | 0       | IF PLL Lock Detect Enable                                           |

|             |           |         | 0=disabled                                                          |

|             |           |         | 1=enabled                                                           |

| IFPLL1(9)   | P1        | 0       | IF PLL Prescaler Modulus                                            |

|             |           |         | 0=4/5 Mode                                                          |

|             |           |         | 1=8/9 Mode                                                          |

| IFPLL1(8:4) | Reserved  | 00000   | Reserved, program to zero (0)                                       |

| IFPLL1(3:0) | DAC1(3:0) | 3h      | IF VCO Coarse Tuning Voltage                                        |

|             |           |         | LPF_V1=int (coarse tuning voltage/V <sub>DD</sub> )x16              |

#### IF PLL Register 2 (IFPLL2)-Address 00010

| Location      | Bit Name   | Default | Function                      |

|---------------|------------|---------|-------------------------------|

| IFPLL2(17:16) | Reserved   | 0       | Reserved, program to zero (0) |

| IFPLL2(15:0)  | IF_N(15:0) | 22h     | IFPLL divide-by-N value       |

#### IF PLL Register 3 (IFPLL3)-Address 00011

| Location     | Bit Name     | Default | Function                                                                        |

|--------------|--------------|---------|---------------------------------------------------------------------------------|

| IFPLL3(17)   | Reserved     | 0       | Reserved, program to zero (0)                                                   |

| IFPLL3(16:8) | DN1(16:8)    | 1FFh    | IF VCO KV Calibration, delta N value (signed 2's complement)<br>DeltaF=DN1/(Fr) |

| IFPLL3(7:4)  | CT_DEF1(3:0) | 7h      | IF VCO Coarse Tuning Value                                                      |

| IFPLL3(3:0)  | KV_DEF1(3:0) | 8h      | IF VCO KV Calibration, default value                                            |

#### RF PLL Register 4 (RFPLL1)-Address 00100

| Location    | Bit Name   | Default | Function                                                            |

|-------------|------------|---------|---------------------------------------------------------------------|

| RFPLL1(17)  | PLL_EN     | 0       | RF PLL Enable                                                       |

|             |            |         | 0=disabled                                                          |

|             |            |         | 1=enabled                                                           |

| RFPLL1(16)  | KV_EN      | 0       | RF PLL KV Calibration Enable                                        |

| . ,         |            |         | 0=disabled                                                          |

|             |            |         | 1=enabled                                                           |

| RFPLL1(15)  | VTC_EN     | 1       | RF PLL Coarse Tune Enable                                           |

|             |            |         | 0=VCO coarse tuning system is disabled                              |

|             |            |         | 1=VCO coarse tuning system is enabled                               |

| RFPLL1(14)  | LPF        | 0       | RF PLL Loop Filter Bypass                                           |

|             |            |         | 0=Internal loop filter is used                                      |

|             |            |         | 1=Internal loop filter is bypassed and External loop filter is used |

| RFPLL1(13)  | CPL        | 0       | RF PLL Charge Pump Leakage Current                                  |

|             |            |         | 0=minimum value                                                     |

|             |            |         | 1=2xminimum value                                                   |

| RFPLL1(12)  | PDP        | 1       | RF PLL Phase Detector Polarity                                      |

|             |            |         | 0=positive, VCO frequency increases with increasing tuning voltage  |

|             |            |         | 1=negative, VCO frequency decreases with increasing tuning voltage  |

| RFPLL1(11)  | AUTOCAL_EN | 0       | RF PLL Auto Calibration Enable                                      |

| . ,         |            |         | 0=disabled                                                          |

|             |            |         | 1=enabled                                                           |

| RFPLL1(10)  | LD_EN      | 0       | RF PLL Lock Detect Enable                                           |

|             |            |         | 0=disabled                                                          |

|             |            |         | 1=enabled                                                           |

| RFPLL1(9)   | Р          | 0       | RF PLL Prescaler Modulus                                            |

|             |            |         | 0=8/9 Mode                                                          |

|             |            |         | 1=8/10 Mode                                                         |

| RFPLL1(8:4) | Reserved   | 00000   | Reserved, program to zero (0)                                       |

| RFPLL1(3:0) | DAC(3:0)   | 3h      | RF VCO Coarse Tuning Voltage                                        |

|             |            |         | LPF_V1=int (coarse tuning voltage/V <sub>DD</sub> )x16              |

#### RF PLL Register 5 (RFPLL2)-Address 00101

| Location     | Bit Name    | Default | Function                 |

|--------------|-------------|---------|--------------------------|

| RFPLL2(17:6) | N2(11:0)    | 5Eh     | RF PLL Divide By N Value |

| RFPLL2(5:0)  | NUM2(23:18) | 0       | RF PLL Numerator Value   |

#### RF PLL Register 6 (RFPLL3)-Address 00110

| Location     | Bit Name   | Default | Function               |

|--------------|------------|---------|------------------------|

| RFPLL3(17:0) | NUM2(17:0) | 0       | RF PLL Numerator Value |

#### RF PLL Register 7 (RFPLL4)-Address 00111

| Location     | Bit Name    | Default | Function                                                                           |

|--------------|-------------|---------|------------------------------------------------------------------------------------|

| RFPLL4(17)   | Reserved    | 0       | Reserved, program to zero (0)                                                      |

| RFPLL4(16:8) | DN(8:0)     | 145 h   | RF VCO KV Calibration, delta N value (signed 2's complement)<br>DN=(deltaF/Fr)*256 |

| RFPLL4(7:4)  | CT_DEF(3:0) | 7h      | RF VCO Coarse Tuning Value                                                         |

| RFPLL4(3:0)  | KV_DEF(3:0) | 8h      | RF VCO KV Calibration, default value                                               |

#### Calibration Register 8 (CAL1)-Address 01000

|             | · · ·               |         |                                                                                                    |

|-------------|---------------------|---------|----------------------------------------------------------------------------------------------------|

| Location    | Bit Name            | Default | Function                                                                                           |

| CAL1(17:13) | TVCO(4:0)           | 0Fh     | VCO1 Warm-up Time<br>TVCO1=(approximate warm-up time)x(Fr/32)                                      |

| CAL1(12:8)  | TLOCK(4:0)          | 07h     | VCO1 Tuning Gain Calibration, approximate lock time<br>TLOCK1=(approximate lock time)x(Fr/128)     |

| CAL1(7:3)   | M_CT_VALUE<br>(4:0) | 08h     | VCO1 Coarse Tune Calibration Reference clock averaging time<br>M_CT_VALUE=(averaging time)x(Fr/32) |

| CAL1(2:0)   | LD_WINDOW<br>(2:0)  | 2h      | Lock Detect Resolution 0 through 7                                                                 |

#### TXRX Register 9 (TXRX1)-Address 01001

| Location     | Bit Name          | Default | Function                                                                                                                                                              |

|--------------|-------------------|---------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| TXRX1(17)    | RXDCFBBYPS        | 0       | Receiver DC Removal Loop<br>0=Enable DC Removal Loop<br>1=Disable DC Removal Loop                                                                                     |

| TXRX1(16:15) | PCONTROL<br>(1:0) | 00      | 00 External TXVGC Controls VGA   01 External TXVGC Controls VGA   10 Internal Control of VGA from Register TXVGC(4:0)   11 Internal Control of VGA from Power Control |

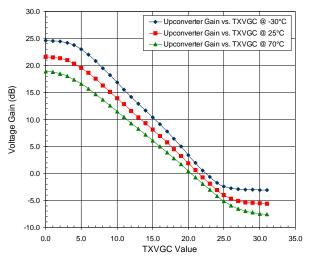

| TXRX1(14:10) | TXVGC(4:0)        | 00000   | Transmit Variable Gain Select<br>0h-1Fh High gain to low gain                                                                                                         |

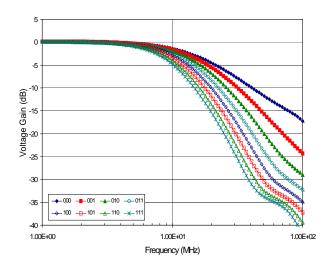

| TXRX1(9:7)   | RXLPFBW<br>(2:0)  | 010     | Receive Baseband Low Pass Filter Bandwidth Selection<br>000=Wide Bandwidth<br>111=Narrow Bandwidth                                                                    |

| TXRX1(6:4)   | TXLPFBW<br>(2:0)  | 010     | Transmit Baseband Low Pass Filter Bandwidth Selection<br>000=Wide Bandwidth<br>111=Narrow Bandwidth                                                                   |

| TXRX1(3)     | TXDIFFMODE        | 0       | Switches Between Single-Ended and Differential Mode<br>0=Single-ended mode<br>1=Differential mode                                                                     |

| TXRX1(2)     | TXENMODE          | 0       | Input Buffer Enable TX<br>0=Input Buffer Controlled by TXEN<br>1=Input Buffer Controlled by BBEN                                                                      |

| TXRX1(1)     | INTBIASEN         | 0       | Internal Bias Enable<br>0=Disabled - External Bias Required<br>1=Enabled - Internal Bias Enabled                                                                      |

| TXRX1(0)     | TXBYPASS          | 0       | TX Baseband Filters Bypass<br>0=Not Bypassed<br>1=Bypassed                                                                                                            |

#### Power Control Register 10 (PCNT1)-Address 01010

| Location     | Bit Name           | Default | Function                                                                                                                                                                                                                    |  |

|--------------|--------------------|---------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| PCNT1(17:15) | MID_BIAS(2:0)      | 000     | Used to setup the voltage provided by the PA_BIAS AMPLIFIER to deter-<br>mine the BIAS VOLTAGE to provide to the PA when the desired output<br>power is MID_POWER. The MID_BIAS selection will select a V <sub>OUT</sub> on |  |

|              |                    |         | PBIAS between 1.6V and 2.6V.                                                                                                                                                                                                |  |

| PCNT1(14:9)  | P_DESIRED<br>(5:0) | 000000  | User selectable desired output power at antenna. The 5 MSB's are integ portion in dBm. The LSB is 0.5dBm. Example: +19.5dBm is represented 100111.                                                                          |  |

| PCNT1(8:3)   | PC_OFFSET<br>(5:0) | 000000  | User programmable offset to adjust to process/board variations in the power control loop. This is a 2's-complement value with the LSB equal to 0.5dB.                                                                       |  |

| PCNT1(2:0)   | TX_DELAY<br>(2:0)  | 000     | User programmable delay to allow a single TX_PE line to be used to enable the BBP and the radio function. Programmable in 0.5 us increments from 0 us to 3.5 us.                                                            |  |

#### Power Control Register 11 (PCNT2)-Address 01011

| Location     | Bit Name           | Default | Function                                                                                                                                                                                                          |

|--------------|--------------------|---------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PCNT2(17:12) | MAX_POWER<br>(5:0) | 000000  | User programmable MAX output power provided when PABIAS=2.6V. This allows the power control function to be customized for various PA's. The 5 MSB's are integer portion in dBm. The LSB is 0.5dBm.                |

| PCNT2(11:6)  | MID_POWER<br>(5:0) | 000000  | User programmable MAX output power provided when<br>PABIAS=MID_BIAS. This allows the power control function to be custom-<br>ized for various PA's. The 5 MSB's are integer portion in dBm. The LSB is<br>0.5dBm. |

| PCNT2(5:0)   | MIN_POWER<br>(5:0) | 000000  | User programmable MAX output power provided when PABIAS=1.6V. This allows the power control function to be customized for various PA's. The 5 MSB's are integer portion in dBm. The LSB is 0.5dBm.                |

#### VCOT1 Register 1 (VCOT1)-Address 01100

| Location    | Bit Name | Default | Function                                                    |  |

|-------------|----------|---------|-------------------------------------------------------------|--|

| VCOT1(17)   | AUX      | 0       | IF VCO Band Current Compensation<br>0=disabled<br>1=enabled |  |

| VCOT1(16)   | AUX1     | 0       | RF VCO Band Current Compensation<br>0=disabled<br>1=enabled |  |

| VCOT1(15:0) | Reserved | 0       | Reserved, program to zero (0)                               |  |

# **Test Register 1 (TEST)-Address 11011** This is a test register for internal use only.

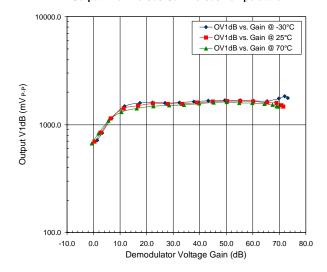

Output V1dB versus Gain versus Temperature

TX/RX Baseband Filter Response

Rev A0 050209

Upconverter Gain versus Analog TXVGC

Upconverter Gain versus Digital TXVGC

Modulator Magnitude Error and Image Suppression

Upconverter P1dB versus Digital TXVGC

### **PCB Design Requirements**

#### PCB Surface Finish

The PCB surface finish used for RFMD's qualification process is Electroless Nickel, immersion Gold. Typical thickness is 3µinch to 8µinch Gold over 180µinch Nickel.

#### **PCB Land Pattern Recommendation**

PCB land patterns are based on IPC-SM-782 standards when possible. The pad pattern shown has been developed and tested for optimized assembly at RFMD; however, it may require some modifications to address company specific assembly processes. The PCB land pattern has been developed to accommodate lead and package tolerances.

#### **PCB Metal Land Pattern**

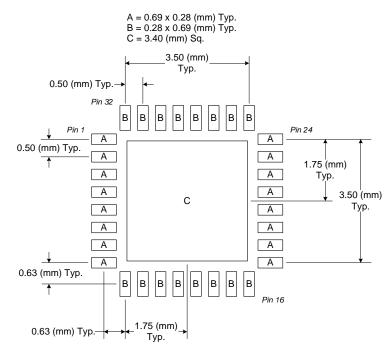

Figure 1. PCB Metal Land Pattern (Top View)

#### PCB Solder Mask Pattern

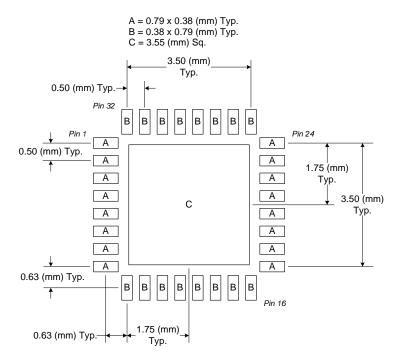

Liquid Photo-Imageable (LPI) solder mask is recommended. The solder mask footprint will match what is shown for the PCB Metal Land Pattern with a 3mil expansion to accommodate solder mask registration clearance around all pads. The center-grounding pad shall also have a solder mask clearance. Expansion of the pads to create solder mask clearance can be provided in the master data or requested from the PCB fabrication supplier.

Figure 2. PCB Solder Mask Pattern (Top View)

#### **Thermal Pad and Via Design**

The PCB Metal Land Pattern has been designed with a thermal pad that matches the exposed die paddle size on the bottom of the device.

Thermal vias are required in the PCB layout to effectively conduct heat away from the package. The via pattern has been designed to address thermal, power dissipation and electrical requirements of the device as well as accommodating routing strategies.

The via pattern used for the RFMD qualification is based on thru-hole vias with 0.203mm to 0.330mm finished hole size on a 0.5mm to 1.2mm grid pattern with 0.025mm plating on via walls. If micro vias are used in a design, it is suggested that the quantity of vias be increased by a 4:1 ratio to achieve similar results.